# Accurate Thermal Modeling of Heterogeneous **Multi-Core Processors**

Darong Huang EPFL, Switzerland Luis Costero UCM, Spain

Federico Terraneo Politecnico di Milano, Italy

Marina Zapater HES-SO, Switzerland

David Atienza EPFL, Switzerland darong.huang@epfl.ch lcostero@ucm.es federico.terraneo@polimi.it marina.zapater@heig-vd.ch david.atienza@epfl.ch

Abstract—The increasing power density of modern multi-core processors using deep nano-scale technologies has entailed severe thermal issues for such chips. Indeed, industry's heterogeneous chip design trends exacerbate transient non-uniform thermal hotspots in next-generation processors. Different cooling solutions are coming into play to alleviate this situation, such as liquid, evaporative, or thermoelectric cooling, among others. Hence, a new generation of thermal simulators with unprecedented flexibility is required to include such technologies in the modeling of nano-scale IC design technologies. This work presents 3D-ICE 3.1, the first thermal simulator designed for fully customized nonuniform modeling and accurate co-simulation with different heat dissipation systems.

## I. Introduction

The race toward boosting performance is consistently pushing the thermal design power (TDP) of high-performance processors exceeding 400W in modern commercial processors [1]. Coupled with non-uniform distribution of power density on the chip, thermal hotspots have become the primary concern in multiprocessor system-on-chip (MPSoC) design, as these hotspots are the root of performance loss and shorten the lifespan of the chip [2]. As computer architectures are becoming increasingly heterogeneous, the trend leads to a more drastically non-uniform distribution of power density, thus further exacerbating concerns on thermal hotspots.

To alleviate the problem of hotspots, heat dissipation saw the first revolution in the Pentium era with fan cooling [3]. The second revolution is now taking place as liquid cooling technologies are implemented in high-performance desktop computers as well as in data centers, and two-phase cooling is on the horizon. However, thermal is still the primary concern to degrade microprocessors' performance and reliability. Hence, thermal simulators play a crucial role in this scenario to model and predict the hotspots for processors. These simulators enable chip designers to effectively and economically perform design space explorations, investigate thermal management schemes, and evaluate different dissipation solutions. However, existing state-of-the-art thermal simulators [4], [5] lack the support for sophisticated heat sink simulations. Besides, these simulators only support uniform thermal modeling.

This work was supported in part by the EC H2020 RECIPE Project under Grant 801137, in part by the ERC Consolidator Grant COMPUSAPIEN under Grant 725657, and in part by a Short Term Collaboration grant for Federico Terraneo with EPFL through EC EUROLAB-4-HPC CSA (Grant no. 800962).

In this work, we introduce 3D-ICE v3.1<sup>1</sup>, a novel opensource thermal simulator designed to perform efficient nonuniform thermal modeling, as well as including an accurate co-simulation with arbitrary heat sink models.

#### II. BACKGROUND

Thermal simulators play an essential role in performing thermal-aware MPSoC design and evaluating thermal management schemes [2], [3]. HotSpot [4] was the first wellknown simulator thanks to its ease of usage in an MPSoC scenario. Then, a generation of simulators, including ISAC [6] and LoCool [5], among others, have been proposed with their specific advantages. Existing thermal simulators [4], [5] use a fixed grid size for the whole chip without discerning thermal hotspots or cold parts. To achieve the best simulation accuracy, the dimension of the thermal grid needs to be small enough to capture the hotspots. Under the uniform modeling paradigm, the same grid size is also applied to structurally colder parts, such as caches of the chip, which, however, do not require high accuracy as hotspots. Thus introducing unnecessary high computation overhead and memory usage by using uniform modeling thermal simulators.

In addition, to the best of our knowledge, existing simulators are monolithic in nature, requiring an extension to the simulator core for adding new heat dissipation models, and as a result, only support simple heat sinks, hindering the simulation of MPSoCs cooled by the latest generation cooling solutions. Therefore, we present in this work how new thermal modeling frameworks, such as 3D-ICE v3.1, including a fully customizable non-uniform thermal modeling method and a co-simulation interface to support arbitrary heat sink models, can appropriately perform accurate modeling and co-design of next-generation heterogeneous computing systems.

# III. NEW THERMAL MODELING TOOLS FOR NANO-SCALE TECHNOLOIGES: 3D-ICE v3.1

## A. Non-uniform thermal modeling

Finite volume, uniform thermal modeling is vastly used in existing thermal simulators [4], [5] thanks to its simplicity. Each thermal grid has connections with its neighbors in six directions, i.e., top, down, north, south, west, east. However, the thermal grid in the non-uniform scenario has

<sup>&</sup>lt;sup>1</sup>https://esl.epfl.ch/3d-ice

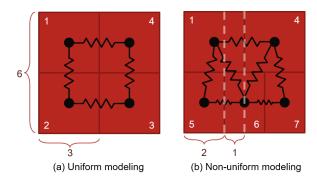

Fig. 1. Different modeling methods

an undetermined number of neighbors because of the non-uniform discretization method. Thus, we apply the Minkowski difference algorithm [7] in 3D-ICE 3.1 to efficiently find interconnected thermal grids.

Next, we utilize the grid pitch adaptation method to calculate the thermal conductance in the non-uniform modeling scenario, where the thermal conductance depends on the interconnect area between two neighboring grids. As Fig. 1 illustrates, the interconnect area between grids 1 and 5 is 2/3 of the area between grids 1 and 2. In this case, the thermal conductance between grids 1 and 5 ( $G_{1,5}$ ) equals 2/3 of  $G_{1,2}$ .

The thermal capacitance is more straightforward to model than thermal conductance, as it is only dependent on the volume of the grid once the material is determined.

Based on the previously discussed non-uniform modeling methods, 3D-ICE v3.1 supports different grid sizes per layer and die. Furthermore, the discretization level for each floorplan element can be further refined in the floorplan description file to accommodate a very diverse set of layouts.

#### B. Co-simulation with different Heat Sink models

We add a co-simulation interface that enables 3D-ICE to connect with arbitrary heat sink models without changing the underlying chip thermal model. The proposed co-simulation interface follows the Functional Mockup Interface (FMI) industry standard [8], which integrates a vast set of languages and tools, including equation-based ones like Modelica and Simscape [9]. Hence, it is possible to create any types of heat sink models directly in terms of the equations describing the underlying physical phenomena. We refer the interested reader to the 3D-ICE 3.0 paper [3] for more details.

# IV. CASE STUDY AND VALIDATION

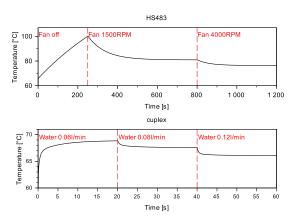

To verify the accuracy of 3D-ICE, we tested it with two different heat sink models (provided with the open-source released version of 3D-ICE 3.1 [10].) addressing air and water cooling. Figure 2 shows the effect of a hotspot in a transient simulation, as well as the impact of using variable coolant flow rate. In this experiment, one heater of the simulated thermal test chip was set to a constant power of 300W/cm<sup>2</sup> for a better study of a sweep of design space alternatives using the variable

Fig. 2. 3D-ICE v3.1 simulation showing the effect of variable coolant flow. The temperature shown here is the one at the hot spot.

coolant flow rates. The hot spot's temperature responds to the variation of heat dissipation conditions in both heat sinks.

The average and maximum error against real measurements across the entire experimental campaign is reported in Table I. Overall, 3D-ICE achieves less than 1°C average error. The non-uniform thermal modeling method introduced in 3D-ICE 3.1 provides users more flexibility on local hotpots analysis without compromising simulation accuracy.

TABLE I

VALIDATION OF THE 3D-ICE AGAINST REAL MEASUREMENTS

| Error   | Air heat sink,  | Air heat sink, | Water heat     |

|---------|-----------------|----------------|----------------|

|         | natural convec. | forced convec. | sink           |

| Average | $0.8^{\circ}C$  | $0.5^{\circ}C$ | $0.9^{\circ}C$ |

| Maximum | $4.1^{\circ}C$  | $3.0^{\circ}C$ | $5.0^{\circ}C$ |

## V. CONCLUSION AND FUTURE WORK

In this work, we have presented 3D-ICE v3.1 as a non-uniform MPSoC thermal simulator supporting different heat dissipation systems. It is developed to simulate hotspots of modern and next-generation heterogeneous MPSoCs thanks to its fully customized non-uniform modeling method. Besides, 3D-ICE 3.1 also supports various sophisticated cooling solutions by virtue of its powerful co-simulation interface. As future work, after releasing the simulator as open-source (https://esl.epfl.ch/3d-ice), we will work with the computer architecture community in extending it in different ways:

- Support asymmetrical thermal conductance in different axes.

- Support an even large range of possible new heat sink models to address the cooling needs of nano-scale chips.

- Extend 3D-ICE to model evaporation in heat sinks. Support will be made available in the near future in the form of a Modelica library. This will allow modeling heat pipes and vapor chambers.

- Embed 3D-ICE with the open-source architectural simulator gem5-X [11] to offer a holistic solution for thermal-aware MPSoC design.

#### REFERENCES

- [1] Intel Xeon Platinum 9282. [Online]. Available: https://ark.intel.com/content/www/us/en/ark/products/194146/intel-xeon-platinum-9282-processor-77m-cache-2-60-ghz.html

- [2] A. Hankin, D. Werner, M. Amiraski, J. Sebot, K. Vaidyanathan, and M. Hempstead, "Hotgauge: A methodology for characterizing advanced hotspots in modern and next generation processors," in 2021 IEEE International Symposium on Workload Characterization (IISWC). IEEE, 2021, pp. 163–175.

- [3] F. Terraneo, A. Leva, W. Fornaciari, M. Zapater Sancho, D. Atienza Alonso et al., "3D-ICE 3.0: efficient nonlinear MPSoC thermal simulation with pluggable heat sink models," *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and Systems, 2021.

- [4] W. Huang, S. Ghosh, S. Velusamy, K. Sankaranarayanan, K. Skadron, and M. R. Stan, "Hotspot: A compact thermal modeling methodology for early-stage vlsi design," *IEEE Transactions on very large scale integration (VLSI) systems*, vol. 14, no. 5, pp. 501–513, 2006.

- [5] F. Kaplan, M. Said, S. Reda, and A. Coskun, "LoCool: Fighting Hot Spots Locally for Improving System Energy Efficiency," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 39, no. 4, pp. 895–908, 2020.

- [6] Y. Yang, Z. Gu, C. Zhu, R. P. Dick, and L. Shang, "ISAC: Integrated space-and-time-adaptive chip-package thermal analysis," *IEEE Transac*tions on Computer-Aided Design of Integrated Circuits and Systems, vol. 26, no. 1, pp. 86–99, 2006.

- [7] H. R. Tiwary, "On the hardness of computing intersection, union and minkowski sum of polytopes," *Discrete & Computational Geometry*, vol. 40, no. 3, pp. 469–479, 2008.

- [8] The Functional Mock-up Interface (FMI) standard. [Online]. Available: https://fmi-standard.org/

- [9] Tools supporting the Functional Mock-up Interface (FMI) standard. [Online]. Available: https://fmi-standard.org/tools/

- [10] 3D-ICE 3.1. [Online]. Available: https://esl.epfl.ch/3d-ice

- [11] Y. M. Qureshi, W. A. Simon, M. Zapater, K. Olcoz, and D. Atienza, "Gem5-x: A many-core heterogeneous simulation platform for architectural exploration and optimization," ACM Transactions on Architecture and Code Optimization (TACO), vol. 18, no. 4, pp. 1–27, 2021.